RISC-V嵌入式开发 (1).pdf

”RISC-V 蜂鸟E203 嵌入式“ 的搜索结果

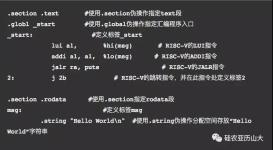

本文将介绍如何直接使用RISC-V架构的汇编语言进行程序设计。

随着国内第一本RISC-V中文书籍《手把手教你设计CPU——RISC-V处理器篇》 正式上市,越来越多的爱好者开始使用开源的蜂鸟E203 RISC-V处理核,很多初学者留言询问有关RISC-V工具链使用的问题,因此本公众号将开始陆续...

RISC-V最近越来越多的出现在科技新闻中,大量的公司加入到RISC-V研究和生产中。在越来越多的RISC-V研究热下,毋容置疑的是RISC-V的时代即将到来。让我们在这浪潮翻滚起来前,一起掀开RISC-V的神秘面纱,提前了解一下...

本文用于记录与学习,参考1.《手把手教你设计CPU.RISC-V处理器》(胡振波)2. b站up主“芯来科技”相关教程3. b站up主“Rong晔”相关教程如有侵权,联系删除。

RISC-V架构生态及相关学习记录

RISC-V架构的中断与异常 一般来说由处理器内部的事件或程序执行中的事件引起的程序跳转称为异常;一般的由处理器外部因素引起的程序跳转称为中断 广义上来说中断和异常都被处理器视为异常,一般将其分为同步异常和...

蜂鸟E203内核是基于两阶段流水线的超低功耗/区域实施,使蜂鸟E203成为RISC-V实施研究和教育的理想之选。 欢迎访问以查看有关Hummingbird E203的讨论。 欢迎访问 ,以可用的RISC-V MCU芯片和嵌入式开

关注+星标公众号,不错过精彩内容转自|痞子衡嵌入式自RISC-V指令集2010年诞生以来,业界普遍认为,RISC-V将会改变现有的由Arm和Intel X86主导的处理器架构竞争格局,...

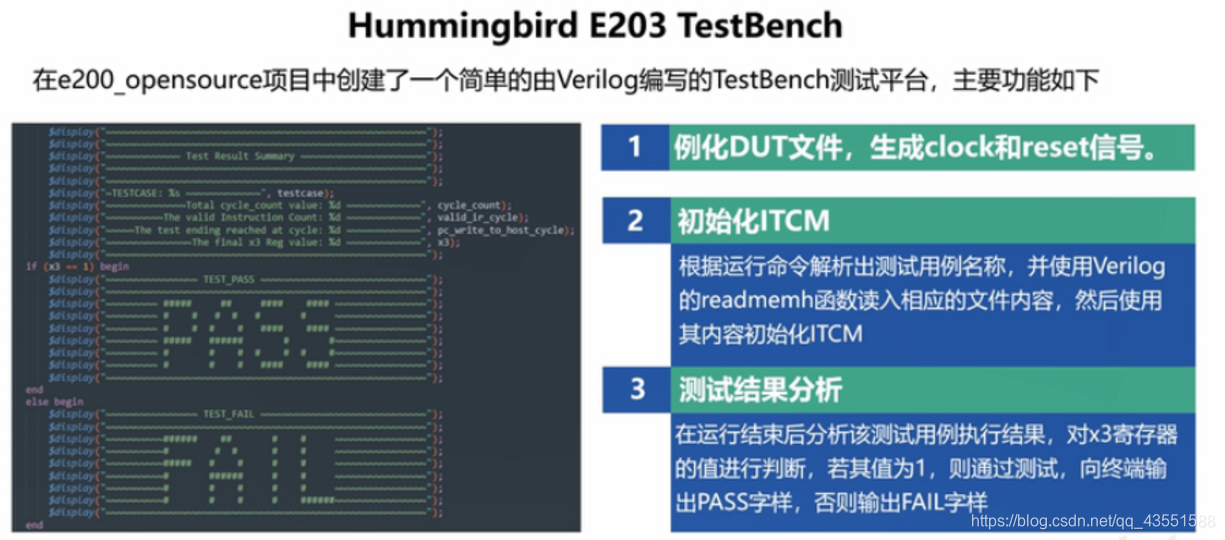

蜂鸟E203的处理器中没有配备缓存,处理器外则分别配备了ITCM和DTCM用于存储指令和数据 虽然在常见的PC的CPU大都配备了缓存,甚至有一二三级不同缓存用来提高内核执行效率,但实际上大部分的低功耗中低性能处理器并...

RISC-V入门学习,书籍,视频及项目推荐

在真正的去了解RISC-V之前,其实我只是在自己关注的一些嵌入式的公众号上看到过关于它的文章,而且看到过很多次,可见它现在真的很火,但是我都没有仔细的去了解过。 ...

RISC-V处理器嵌入式开发 时间地点 时间:3月1日起,每周周一、周四的13:30-14:30 地点:网络授课 面向人群:对RISC-V以及软件开发和CPU设计感兴趣的工程师、开发者、爱好者和学生 课程表 一共8节课,...

本文介绍了RV32I的基本指令格式及内容,为之后进行处理器的实现打下了基础。

推荐文章

- 大数据技术未来发展前景及趋势分析_大数据技术的发展方向-程序员宅基地

- Abaqus学习-初识Abaqus(悬臂梁)_abaqus悬臂梁-程序员宅基地

- 数据预处理--数据格式csv、arff等之间的转换_csv转arff文件-程序员宅基地

- c语言发送网络请求,如何使用C+发出HTTP请求?-程序员宅基地

- ccc计算机比赛如何报名,整理:加拿大的CCC是什么,怎么报名?-程序员宅基地

- RK3568 学习笔记 : ubuntu 20.04 下 Linux-SDK 镜像烧写_rk3568刷linux-程序员宅基地

- Gradle是什么_gradle是干嘛的-程序员宅基地

- adb命令集锦-程序员宅基地

- 【Java基础学习打卡15】分隔符、标识符与关键字_java分隔符有哪三种-程序员宅基地

- Python批量改变图片名字_python批量修改图片名称-程序员宅基地